#### UNIT – I

#### **Number System and Codes**

- Binary number system

- Binary to Decimal

- Decimal to Binary

- Hexadecimal

- Ascii code

- Excess-3 Code

- Gray Code

#### **Digital Logic**

- Basic Gates- AND, OR, NOT

- Universal Logic Gates- NOR, NAND

-----

## **NUMBER SYSTEM AND CODES**

In a digital system, the system can understand only the optional number system. In these systems, digits symbols are used to represent different values, depending on the index from which it settled in the number system.

In simple terms, for representing the information, we use the number system in the digital system.

The digit value in the number system is calculated using:

- 1. The digit

- 2. The index, where the digit is present in the number.

- 3. Finally, the base numbers, the total number of digits available in the number system.

#### **Types of Number System**

In the digital computer, there are various types of number systems used for representing information.

- 1. Binary Number System

- 2. Decimal Number System

- 3. Hexadecimal Number System

- 4. Octal Number System

# **Binary Number System**

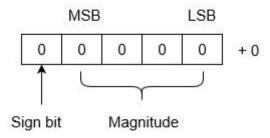

Generally, a binary number system is used in the digital computers. In this number system, it carries only two digits, either 0 or 1. There are two types of electronic pulses present in a binary number system. The first one is the absence of an electronic pulse representing '0'and second one is the presence of electronic pulse representing '1'. Each digit is known as a bit. A four-bit collection (1101) is known as a nibble, and a collection of eight

bits (11001010) is known as a byte. The location of a digit in a binary number represents a specific power of the base (2) of the number system.

#### **Characteristics:**

- 1. It holds only two values, i.e., either 0 or 1.

- 2. It is also known as the base 2 number system.

- 3. The position of a digit represents the 0 power of the base(2). Example:  $2^0$

- 4. The position of the last digit represents the x power of the base(2). Example:  $2^x$ , where x represents the last position, i.e., 1

## **Examples:**

```

(10100)_2, (11011)_2, (11001)_2, (000101)_2, (011010)_2.

```

## **Decimal Number System**

The decimal numbers are used in our day to day life. The decimal number system contains ten digits from 0 to 9(base 10). Here, the successive place value or position, left to the decimal point holds units, tens, hundreds, thousands, and so on.

The position in the decimal number system specifies the power of the base (10). The 0 is the minimum value of the digit, and 9 is the maximum value of the digit. For example, the decimal number 2541 consist of the digit 1 in the unit position, 4 in the tens position, 5 in the hundreds position, and 2 in the thousand positions and the value will be written as:

$$(2\times1000) + (5\times100) + (4\times10) + (1\times1)$$

$(2\times10^3) + (5\times10^2) + (4\times10^1) + (1\times10^0)$

$2000 + 500 + 40 + 1$

$2541$

#### **Octal Number System**

The octal number system has base 8(means it has only eight digits from 0 to 7). There are only eight possible digit values to represent a number. With the help of only three bits, an octal number is represented. Each set of bits has a distinct value between 0 and 7.

Below, we have described certain characteristics of the octal number system:

#### **Characteristics:**

- 1. An octal number system carries eight digits starting from 0, 1, 2, 3, 4, 5, 6, and 7.

- 2. It is also known as the base 8 number system.

- 3. The position of a digit represents the 0 power of the base(8). Example:  $8^{0}$

- 4. The position of the last digit represents the x power of the base(8). Example: 8<sup>x</sup>, where x represents the last position, i.e., 1

| Number | Octal Number |

|--------|--------------|

| 0      | 000          |

| 1      | 001          |

| 2      | 010          |

| 3      | 011          |

| 4      | 100          |

| 5      | 101          |

| 6      | 110          |

| 7      | 111          |

## **Examples:**

$(273)_8$ ,  $(5644)_8$ ,  $(0.5365)_8$ ,  $(1123)_8$ ,  $(1223)_8$ .

# **Hexadecimal Number System**

It is another technique to represent the number in the digital system called the **hexadecimal number system**. The number system has a base of 16 means there are total 16 symbols(0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F) used for representing a number. The single-bit representation of decimal values10, 11, 12, 13, 14, and 15 are represented by A, B, C, D, E, and F. Only 4 bits are required for representing a number in a hexadecimal number. Each set of bits has a distinct value between 0 and 15. There are the following characteristics of the octal number system:

### **Characteristics:**

- 1. It has ten digits from 0 to 9 and 6 letters from A to F.

- 2. The letters from A to F defines numbers from 10 to 15.

- 3. It is also known as the base 16number system.

- 4. In hexadecimal number, the position of a digit represents the 0 power of the base(16). Example: 16<sup>0</sup>

- 5. In hexadecimal number, the position of the last digit represents the x power of the base(16). Example: 16<sup>x</sup>, where x represents the last position, i.e., 1

| Binary Number | Hexadecimal Number |

|---------------|--------------------|

| 0000          | 0                  |

| 0001          | 1                  |

| 0010          | 2                  |

| 0011 | 3 |

|------|---|

| 0100 | 4 |

| 0101 | 5 |

| 0110 | 6 |

| 0111 | 7 |

| 1000 | 8 |

| 1001 | 9 |

| 1010 | A |

| 1011 | В |

| 1100 | C |

| 1101 | D |

| 1110 | E |

| 1111 | F |

### **Examples:**

(FAC2)<sub>16</sub>, (564)<sub>16</sub>, (0ABD5)<sub>16</sub>, (1123)<sub>16</sub>, (11F3)<sub>16</sub>.

# **Number Base Conversion**

Types of number systems are binary, decimal, octal, and hexadecimal. In this part, we will learn how we can change a number from one number system to another number system.

As, we have four types of number systems so each one can be converted into the remaining three systems. There are the following conversions possible in Number System

- 1. Binary to other Number Systems.

- 2. Decimal to other Number Systems.

- 3. Octal to other Number Systems.

- 4. Hexadecimal to other Number Systems.

# **Binary to other Number Systems**

There are three conversions possible for binary number, i.e., binary to decimal, binary to octal, and binary to hexadecimal. The conversion process of a binary number to decimal differs from the remaining others. Let's take a detailed discussion on Binary Number System conversion.

## **Binary to Decimal Conversion**

The process of converting binary to decimal is quite simple. The process starts from multiplying the bits of binary number with its corresponding positional weights. And lastly, we add all those products.

Let's take an example to understand how the conversion is done from binary to decimal.

## Example: (10110.001)<sub>2</sub>

We multiplied each bit of  $(10110.001)_2$  with its respective positional weight, and last we add the products of all the bits with its weight.

```

\begin{array}{c} (10110.001)_2 = (1 \times 24) + (0 \times 23) + (1 \times 22) + (1 \times 21) + (0 \times 20) + \\ (0 \times 2 - 1) + (0 \times 2 - 2) + (1 \times 2 - 3) \\ (10110.001)_2 = (1 \times 16) + (0 \times 8) + (1 \times 4) + (1 \times 2) + (0 \times 1) + \\ (0 \times 1/2) + (0 \times 1/4) + (1 \times 1/8) \\ (10110.001)_2 = 16 + 0 + 4 + 2 + 0 + 0 + 0 + 0 + 125 \\ (10110.001)_2 = (22.125)_{10} \end{array}

```

## **Binary to Octal Conversion**

The base numbers of binary and octal are 2 and 8, respectively. In a binary number, the pair of three bits is equal to one octal digit. There are only two steps to convert a binary number into an octal number which are as follows:

- 1. In the first step, we have to make the pairs of three bits on both sides of the binary point. If there will be one or two bits left in a pair of three bits pair, we add the required number of zeros on extreme sides.

- 2. In the second step, we write the octal digits corresponding to each pair.

## Example: (111110101011.0011)<sub>2</sub>

1. Firstly, we make pairs of three bits on both sides of the binary point.

```

111 110 101 011.001 1

```

On the right side of the binary point, the last pair has only one bit. To make it a complete pair of three bits, we added two zeros on the extreme side.

```

111 110 101 011.001 100

```

2. Then, we wrote the octal digits, which correspond to each pair.

#### $(111110101011.0011)_2 = (7653.14)_8$

#### **Binary to Hexadecimal Conversion**

The base numbers of binary and hexadecimal are 2 and 16, respectively. In a binary number, the pair of four bits is equal to one hexadecimal digit. There are also only two steps to convert a binary number into a hexadecimal number which are as follows:

- 1. In the first step, we have to make the pairs of four bits on both sides of the binary point. If there will be one, two, or three bits left in a pair of four bits pair, we add the required number of zeros on extreme sides.

- 2. In the second step, we write the hexadecimal digits corresponding to each pair.

## Example: (10110101011.0011)<sub>2</sub>

1. Firstly, we make pairs of four bits on both sides of the binary point.

111 1010 1011.0011

On the left side of the binary point, the first pair has three bits. To make it a complete pair of four bits, add one zero on the extreme side.

0111 1010 1011.0011

2. Then, we write the hexadecimal digits, which correspond to each pair.

$(011110101011.0011)_2 = (7AB.3)_{16}$

## **Decimal to other Number System**

The decimal number can be an integer or floating-point integer. When the decimal number is a floating-point integer, then we convert both part (integer and fractional) of the decimal number in the isolated form(individually). There are the following steps that are used to convert the decimal number into a similar number of any base 'r'.

- 1. In the first step, we perform the division operation on integer and successive part with base 'r'. We will list down all the remainders till the quotient is zero. Then we find out the remainders in reverse order for getting the integer part of the equivalent number of base 'r'. In this, the least and most significant digits are denoted by the first and the last remainders.

- 2. In the next step, the multiplication operation is done with base 'r' of the fractional and successive fraction. The carries are noted until the result is zero or when the required number of the equivalent digit is obtained. For getting the fractional part of the equivalent number of base 'r', the normal sequence of carrying is considered.

## **Decimal to Binary Conversion**

For converting decimal to binary, there are two steps required to perform, which are as follows:

1. In the first step, we perform the division operation on the integer and the successive quotient with the base of binary(2).

2. Next, we perform the multiplication on the integer and the successive quotient with the base of binary(2).

Example: (152.25)<sub>10</sub>

Step 1:

Divide the number 152 and its successive quotients with base 2.

| Operation | Quotient | Remainder |

|-----------|----------|-----------|

| 152/2     | 76       | 0 (LSB)   |

| 76/2      | 38       | 0         |

| 38/2      | 19       | 0         |

| 19/2      | 9        | 1         |

| 9/2       | 4        | 1         |

| 4/2       | 2        | 0         |

| 2/2       | 1        | 0         |

| 1/2       | 0        | 1(MSB)    |

## $(152)_{10} = (10011000)_2$

## **Step 2:**

Now, perform the multiplication of 0.27 and successive fraction with base 2.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×2    | 0.50   | 0     |

| 0.50×2    | 0      | 1     |

$(0.25)_{10} = (.01)_2$

## **Decimal to Octal Conversion**

For converting decimal to octal, there are two steps required to perform, which are as follows:

- 1. In the first step, we perform the division operation on the integer and the successive quotient with the base of octal(8).

- 2. Next, we perform the multiplication on the integer and the successive quotient with the base of octal(8).

Example: (152.25)<sub>10</sub>

# Step 1:

Divide the number 152 and its successive quotients with base 8.

| Operation | Quotient | Remainder |

|-----------|----------|-----------|

| 152/8     | 19       | 0         |

| 19/8      | 2        | 3         |

| 2/8       | 0        | 2         |

$(152)_{10}=(230)_8$

## Step 2:

Now perform the multiplication of 0.25 and successive fraction with base 8.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×8    | 0      | 2     |

# $(0.25)_{10}=(2)_8$

So, the octal number of the decimal number 152.25 is 230.2

### **Decimal to hexadecimal conversion**

For converting decimal to hexadecimal, there are two steps required to perform, which are as follows:

- 1. In the first step, we perform the division operation on the integer and the successive quotient with the base of hexadecimal (16).

- 2. Next, we perform the multiplication on the integer and the successive quotient with the base of hexadecimal (16).

Example: (152.25)<sub>10</sub>

### Step 1:

Divide the number 152 and its successive quotients with base 8.

| Operation | Quotient | Remainder |

|-----------|----------|-----------|

| 152/16    | 9        | 8         |

| 9/16 |  | 9 |

|------|--|---|

|------|--|---|

$(152)_{10} = (98)_{16}$

## Step 2:

Now perform the multiplication of 0.25 and successive fraction with base 16.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×16   | 0      | 4     |

$(0.25)_{10}=(4)_{16}$

So, the hexadecimal number of the decimal number 152.25 is 230.4.

#### **Octal to other Number System**

Like binary and decimal, the octal number can also be converted into other number systems. The process of converting octal to decimal differs from the remaining one. Let's start understanding how conversion is done.

## **Octal to Decimal Conversion**

The process of converting octal to decimal is the same as binary to decimal. The process starts from multiplying the digits of octal numbers with its corresponding positional weights. And lastly, we add all those products.

Let's take an example to understand how the conversion is done from octal to decimal.

Example: (152.25)8

#### Step 1:

We multiply each digit of **152.25** with its respective positional weight, and last we add the products of all the bits with its weight.

$$(152.25)_8$$

= $(1\times8^2)$ + $(5\times8^1)$ + $(2\times8^0)$ + $(2\times8^{-1})$ + $(5\times8^{-2})$

$(152.25)_8$ = $64$ + $40$ + $2$ + $(2\times1/8)$ + $(5\times1/64)$

$(152.25)_8$ = $64$ + $40$ + $2$ + $0.25$ + $0.078125$

$(152.25)_8$ = $106.328125$

So, the decimal number of the octal number 152.25 is **106.328125**

## **Octal to Binary Conversion**

The process of converting octal to binary is the reverse process of binary to octal. We write the three bits binary code of each octal number digit.

## Example: (152.25)8

We write the three-bit binary digit for 1, 5, 2, and 5.

$(152.25)_8 = (001101010.010101)_2$

So, the binary number of the octal number 152.25 is (001101010.010101)<sub>2</sub>

# Octal to hexadecimal conversion

For converting octal to hexadecimal, there are two steps required to perform, which are as follows:

- 1. In the first step, we will find the binary equivalent of number 25.

- 2. Next, we have to make the pairs of four bits on both sides of the binary point. If there will be one, two, or three bits left in a pair of four bits pair, we add the required number of zeros on extreme sides and write the hexadecimal digits corresponding to each pair.

Example: (152.25)8

# Step 1:

We write the three-bit binary digit for 1, 5, 2, and 5.

$(152.25)_8 = (001101010.010101)_2$

So, the binary number of the octal number 152.25 is (001101010.010101)<sub>2</sub>

## Step 2:

1. Now, we make pairs of four bits on both sides of the binary point.

0 0110 1010.0101 01

On the left side of the binary point, the first pair has only one digit, and on the right side, the last pair has only two-digit. To make them complete pairs of four bits, add zeros on extreme sides.

0000 0110 1010.0101 0100

2. Now, we write the hexadecimal digits, which correspond to each pair.

$(0000 \quad 0110 \quad 1010.0101 \quad 0100)_2 = (6A.54)_{16}$

### Hexa-decimal to other Number System

Like binary, decimal, and octal, hexadecimal numbers can also be converted into other number systems. The process of converting hexadecimal to decimal differs from the remaining one. Let's start understanding how conversion is done.

## **Hexa-decimal to Decimal Conversion**

The process of converting hexadecimal to decimal is the same as binary to decimal. The process starts from multiplying the digits of hexadecimal numbers with its corresponding positional weights. And lastly, we add all those products.

Let's take an example to understand how the conversion is done from hexadecimal to decimal.

Example: (152A.25)<sub>16</sub>

## Step 1:

We multiply each digit of **152A.25** with its respective positional weight, and last we add the products of all the bits with its weight.

```

(152A.25)_{16}=(1\times16^3)+(5\times16^2)+(2\times16^1)+(A\times16^0)+(2\times16^{-1})+(5\times16^{-2})

(152A.25)_{16}=(1\times4096)+(5\times256)+(2\times16)+(10\times1)+(2\times16^{-1})+(5\times16^{-2})

(152A.25)_{16}=4096+1280+32+10+(2\times1/16)+(5\times1/256)

(152A.25)_{16}=5418+0.125+0.125

(152A.25)_{16}=5418.14453125

```

So, the decimal number of the hexadecimal number 152A.25 is **5418.14453125**

### **Hexadecimal to Binary Conversion**

The process of converting hexadecimal to binary is the reverse process of binary to hexadecimal. We write the four bits binary code of each hexadecimal number digit.

Example:  $(152A.25)_{16}$

We write the four-bit binary digit for 1, 5, A, 2, and 5.

$(152A.25)_{16} = (0001\ 0101\ 0010\ 1010.0010\ 0101)_2$

So, the binary number of the hexadecimal number 152.25 is (1010100101010.00100101)<sub>2</sub>

### **Hexadecimal to Octal Conversion**

For converting hexadecimal to octal, there are two steps required to perform, which are as follows:

1. In the first step, we will find the binary equivalent of the hexadecimal number.

2. Next, we have to make the pairs of three bits on both sides of the binary point. If there will be one or two bits left in a pair of three bits pair, we add the required number of zeros on extreme sides and write the octal digits corresponding to each pair.

Example: (152A.25)<sub>16</sub>

## Step 1:

We write the four-bit binary digit for 1, 5, 2, A, and 5.

#### $(152A.25)_{16} = (0001\ 0101\ 0010\ 1010.0010\ 0101)_2$

So, the binary number of hexadecimal number 152A.25 is (001101010101010101)<sub>2</sub>

## Step 2:

3. Then, we make pairs of three bits on both sides of the binary point.

001 010 100 101 010.001 001 010

4. Then, we write the octal digit, which corresponds to each pair.

## $(0010101010101010.001001010)_2 = (12452.112)_8$

So, the octal number of the hexadecimal number 152A.25 is 12452.112

## **Gray Code**

The **Gray Code** is a sequence of binary number systems, which is also known as **reflected binary code**. The reason for calling this code as reflected binary code is the first N/2 values compared with those of the last N/2 values in reverse order. In this code, two consecutive values are differed by one bit of binary digits. Gray codes are used in the general sequence of hardware-generated binary numbers. These numbers cause ambiguities or errors when the transition from one number to its successive is done. This code simply solves this problem by changing only one bit when the transition is between numbers is done.

The gray code is a very light weighted code because it doesn't depend on the value of the digit specified by the position. This code is also called a cyclic variable code as the transition of one value to its successive value carries a change of one bit only.

### How to generate Gray code?

The prefix and reflect method are recursively used to generate the Gray code of a number. For generating gray code:

- 1. We find the number of bits required to represent a number.

- 2. Next, we find the code for 0, i.e., 0000, which is the same as binary.

- 3. Now, we take the previous code, i.e., 0000, and change the most significant bit of it.

- 4. We perform this process reclusively until all the codes are not uniquely identified.

5. If by changing the most significant bit, we find the same code obtained previously, then the second most significant bit will be changed, and so on.

# **Gray Code Table**

| Decimal Number | Binary Number | Gray Code |

|----------------|---------------|-----------|

| 0              | 0000          | 0000      |

| 1              | 0001          | 0001      |

| 2              | 0010          | 0011      |

| 3              | 0011          | 0010      |

| 4              | 0100          | 0110      |

| 5              | 0101          | 0111      |

| 6              | 0110          | 0101      |

| 7              | 0111          | 0100      |

| 8              | 1000          | 1100      |

| 9              | 1001          | 1101      |

| 10             | 1010          | 1111      |

| 11             | 1011          | 1110      |

| 12             | 1100          | 1010      |

| 13             | 1101          | 1011      |

| 14             | 1110          | 1001      |

| 15             | 1111          | 1000      |

### Excess-3 Code

The excess-3 code is also treated as **XS-3 code**. The excess-3 code is a non-weighted and self-complementary BCD code used to represent the decimal numbers. This code has a biased representation. This code plays an important role in arithmetic operations because it resolves deficiencies encountered when we use the 8421 BCD code for adding two decimal digits whose sum is greater than 9. The Excess-3 code uses a special type of algorithm, which differs from the binary positional number system or normal non-biased BCD.

We can easily get an excess-3 code of a decimal number by simply adding 3 to each decimal digit. And then we write the 4-bit binary number for each digit of the decimal number. We can find the excess-3 code of the given binary number by using the following steps:

- 1. We find the decimal number of the given binary number.

- 2. Then we add 3 in each digit of the decimal number.

- 3. Now, we find the binary code of each digit of the newly generated decimal number.

We can also add 0011 in each 4-bit BCD code of the decimal number for getting excess-3 code.

### The Excess-3 code for the decimal number is as follows:

| Decimal Digit | BCD Code | Excess-3 Code |

|---------------|----------|---------------|

| 0             | 0000     | 0011          |

| 1             | 0001     | 0100          |

| 2             | 0010     | 0101          |

| 3             | 0011     | 0110          |

| 4             | 0100     | 0111          |

| 5             | 0101     | 1000          |

| 6             | 0110     | 1001          |

| 7             | 0111     | 1010          |

| 8             | 1000     | 1011          |

| 9             | 1001     | 1100          |

In excess-3 code, the codes 1111 and 0000 are never used for any decimal digit. Let's take some examples of Excess-3 code.

# **Example: Decimal number 31**

1. We find the BCD code of each digit of the decimal number.

| Digit | BCD  |

|-------|------|

| 3     | 0011 |

| 1     | 0001 |

2) Then, we add 0011 in both of the BCD code.

| Decimal | BCD       | Excess-3 |

|---------|-----------|----------|

| 3       | 0011+0011 | 0110     |

| 1 0001+ | 0011 0 | 100 |

|---------|--------|-----|

|---------|--------|-----|

3. So, the excess-3 code of the decimal number 31 is **0110 0100**

# **Example: Decimal number 81.61**

1. We find the BCD code of each digit of the decimal number.

| Digit | BCD  |

|-------|------|

| 8     | 1000 |

| 1     | 0001 |

| 6     | 0110 |

| 1     | 0001 |

2) Then, we add 0011 in both of the BCD code.

| Decimal | BCD       | Excess-3 |

|---------|-----------|----------|

| 8       | 1000+0011 | 1011     |

| 1       | 0001+0011 | 0100     |

| 6       | 0110+0011 | 1001     |

3) So, the excess-3 code of the decimal number 81.61 is **1011 0100.1001 0100**

### **ASCII CODE**

The ASCII stands for American Standard Code for Information Interchange. The ASCII code is an alphanumeric code used for data communication in digital computers. The ASCII is a 7-bit code capable of representing 2<sup>7</sup> or 128 number of different characters. The ASCII code is made up of a three-bit group, which is followed by a four-bit code.

- The ASCII Code is a 7 or 8-bit alphanumeric code.

- This code can represent 127 unique characters.

- The ASCII code starts from 00h to 7Fh. In this, the code from 00h to 1Fh is used for control characters, and the code from 20h to 7Fh is used for graphic symbols.

- The 8-bit code holds ASCII, which supports 256 symbols where math and graphic symbols are added.

- The range of the extended ASCII is 80h to FFh.

#### **Basic Gates**

The basic gates are AND, OR & NOT gates.

## **AND** gate

An AND gate is a digital circuit that has two or more inputs and produces an output, which is the **logical AND** of all those inputs. It is optional to represent the **Logical AND** with the symbol '.'.

The following table shows the **truth table** of 2-input AND gate.

| A | В | Y = A.B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

Here A, B are the inputs and Y is the output of two input AND gate. If both inputs are '1', then only the output, Y is '1'. For remaining combinations of inputs, the output, Y is '0'.

The following figure shows the **symbol** of an AND gate, which is having two inputs A, B and one output, Y.

This AND gate produces an output (Y), which is the **logical AND** of two inputs A, B. Similarly, if there are 'n' inputs, then the AND gate produces an output, which is the logical AND of all those inputs. That means, the output of AND gate will be '1', when all the inputs are '1'.

### OR gate

An OR gate is a digital circuit that has two or more inputs and produces an output, which is the logical OR of all those inputs. This **logical OR** is represented with the symbol '+'.

The following table shows the **truth table** of 2-input OR gate.

| A | В | $\mathbf{Y} = \mathbf{A} + \mathbf{B}$ |

|---|---|----------------------------------------|

| 0 | 0 | 0                                      |

| 0 | 1 | 1                                      |

| 1 | 0 | 1                                      |

| 1 | 1 | 1                                      |

Here A, B are the inputs and Y is the output of two input OR gate. If both inputs are '0', then only the output, Y is '0'. For remaining combinations of inputs, the output, Y is '1'.

The following figure shows the **symbol** of an OR gate, which is having two inputs A, B and one output, Y.

This OR gate produces an output (Y), which is the **logical OR** of two inputs A, B. Similarly, if there are 'n' inputs, then the OR gate produces an output, which is the logical OR of all those inputs. That means, the output of an OR gate will be '1', when at least one of those inputs is '1'.

### **NOT** gate

A NOT gate is a digital circuit that has single input and single output. The output of NOT gate is the **logical inversion** of input. Hence, the NOT gate is also called as inverter.

The following table shows the **truth table** of NOT gate.

| A | Y = A' |

|---|--------|

| 0 | 1      |

| 1 | 0      |

Here A and Y are the input and output of NOT gate respectively. If the input, A is '0', then the output, Y is '1'. Similarly, if the input, A is '1', then the output, Y is '0'.

The following figure shows the **symbol** of NOT gate, which is having one input, A and one output, Y.

This NOT gate produces an output (Y), which is the **complement** of input, A.

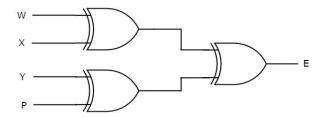

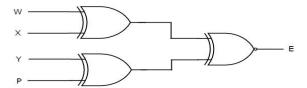

#### **Universal gates**

NAND & NOR gates are called as **universal gates**. Because we can implement any Boolean function, which is in sum of products form by using NAND gates alone. Similarly, we can implement any Boolean function, which is in product of sums form by using NOR gates alone.

### NAND gate

NAND gate is a digital circuit that has two or more inputs and produces an output, which is the **inversion of logical AND** of all those inputs.

The following table shows the **truth table** of 2-input NAND gate.

| A | В | Y = (A.B) |

|---|---|-----------|

| 0 | 0 | 1         |

| 0 | 1 | 1 |

|---|---|---|

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Here A, B are the inputs and Y is the output of two input NAND gate. When both inputs are '1', the output, Y is '0'. If at least one of the input is zero, then the output, Y is '1'. This is just opposite to that of two input AND gate operation.

The following image shows the **symbol** of NAND gate, which is having two inputs A, B and one output, Y.

NAND gate operation is same as that of AND gate followed by an inverter. That's why the NAND gate symbol is represented like that.

### **NOR** gate

NOR gate is a digital circuit that has two or more inputs and produces an output, which is the **inversion of logical OR** of all those inputs.

The following table shows the **truth table** of 2-input NOR gate

| A | В | $\mathbf{Y} = (\mathbf{A} + \mathbf{B})^{\prime}$ |

|---|---|---------------------------------------------------|

| 0 | 0 | 1                                                 |

| 0 | 1 | 0                                                 |

| 1 | 0 | 0                                                 |

| 1 | 1 | 0                                                 |

Here A, B are the inputs and Y is the output. If both inputs are '0', then the output, Y is '1'. If at least one of the input is '1', then the output, Y is '0'. This is just opposite to that of two input OR gate operation.

The following figure shows the **symbol** of NOR gate, which is having two inputs A, B and one output, Y.

NOR gate operation is same as that of OR gate followed by an inverter. That's why the NOR gate symbol is represented like that.

### **REVIEW QUESTIONS**

1) Define Ascii code.

- 2) Define gray code.

- 3) Explain binary to decimal conversion.

- 4) Define hexadecimal.

- 5) Explain about universal logic gates.

- 6) Define excess-3 code.

- 7) Define AND gate.

- 8) Explain binary to octal conversion.

## UNIT – II

# **Combinational Logic Circuits**

- Boolean Laws and Theorems

- Sum of Product Method

- Karnaugh Map

- Pair, Quad and Octet

- Don't Care Condition

- Product of Sum Method

- Product of Sum Simplification

### **Data Processing Circuit**

- Multiplexer

- De-Multiplexer

- 1-of-16 Decoder

- BCD to Decimal Decoder

- Seven Segment Decoders

- Encoders

- Exclusive OR Gates

- Parity Generator and checker

\_\_\_\_\_

## **COMBINATIONAL LOGIC CIRCUIT**

# **Boolean Laws and Theorems**

**Boolean Algebra** is an algebra, which deals with binary numbers & binary variables. Hence, it is also called as Binary Algebra or logical Algebra. A mathematician, named George Boole had developed this algebra in 1854. The variables used in this algebra are also called as Boolean variables.

The range of voltages corresponding to Logic 'High' is represented with '1' and the range of voltages corresponding to logic 'Low' is represented with '0'.

## Postulates and Basic Laws of Boolean Algebra

In this section, let us discuss about the Boolean postulates and basic laws that are used in Boolean algebra. These are useful in minimizing Boolean functions.

#### **Boolean Postulates**

Consider the binary numbers 0 and 1, Boolean variable (x) and its complement (x'). Either the Boolean variable or complement of it is known as **literal**. The four possible **logical OR** operations among these literals and binary numbers are shown below.

$$x + 0 = x$$

$$x + 1 = 1$$

$$x + x = x$$

$$x + x' = 1$$

Similarly, the four possible **logical AND** operations among those literals and binary numbers are shown below.

$$x.1 = x$$

$$x.0 = 0$$

$$x.x = x$$

$$x.x' = 0$$

These are the simple Boolean postulates. We can verify these postulates easily, by substituting the Boolean variable with '0' or '1'.

**Note**— The complement of complement of any Boolean variable is equal to the variable itself. i.e., (x')'=x.

## **Basic Laws of Boolean Algebra**

Following are the three basic laws of Boolean Algebra.

- Commutative law

- Associative law

- Distributive law

# **Commutative Law**

If any logical operation of two Boolean variables give the same result irrespective of the order of those two variables, then that logical operation is said to be **Commutative**. The logical OR & logical AND operations of two Boolean variables x & y are shown below

$$\mathbf{x} + \mathbf{y} = \mathbf{y} + \mathbf{x}$$

$$\mathbf{x} \cdot \mathbf{y} = \mathbf{y} \cdot \mathbf{x}$$

The symbol '+' indicates logical OR operation. Similarly, the symbol '.' indicates logical AND operation and it is optional to represent. Commutative law obeys for logical OR & logical AND operations.

### **Associative Law**

If a logical operation of any two Boolean variables is performed first and then the same operation is performed with the remaining variable gives the same result, then that

logical operation is said to be **Associative**. The logical OR & logical AND operations of three Boolean variables x, y & z are shown below.

$$x + (y + z) = (x + y) + z$$

$x.(y.z) = (x.y).z$

Associative law obeys for logical OR & logical AND operations.

#### **Distributive Law**

If any logical operation can be distributed to all the terms present in the Boolean function, then that logical operation is said to be **Distributive**. The distribution of logical OR & logical AND operations of three Boolean variables x, y & z are shown below.

$$x.(y + z) = x.y + x.z$$

$x + (y.z) = (x + y).(x + z)$

Distributive law obeys for logical OR and logical AND operations.

These are the Basic laws of Boolean algebra. We can verify these laws easily, by substituting the Boolean variables with '0' or '1'.

#### **Theorems of Boolean Algebra**

The following two theorems are used in Boolean algebra.

- Duality theorem

- DeMorgan's theorem

## **Duality Theorem**

This theorem states that the **dual** of the Boolean function is obtained by interchanging the logical AND operator with logical OR operator and zeros with ones. For every Boolean function, there will be a corresponding Dual function.

Let us make the Boolean equations (relations) that we discussed in the section of Boolean postulates and basic laws into two groups. The following table shows these two groups.

| Group1                         | Group2   |

|--------------------------------|----------|

| x + 0 = x                      | x.1 = x  |

| x + 1 = 1                      | x.0 = 0  |

| x + x = x                      | x.x = x  |

| $\mathbf{x} + \mathbf{x'} = 1$ | x.x' = 0 |

| x + y = y + x             | x.y = y.x                   |

|---------------------------|-----------------------------|

| x + (y + z) = (x + y) + z | x.(y.z) = (x.y).z           |

| x.(y+z) = x.y + x.z       | x + (y.z) = (x + y).(x + z) |

In each row, there are two Boolean equations and they are dual to each other. We can verify all these Boolean equations of Group1 and Group2 by using duality theorem.

## **DeMorgan's Theorem**

This theorem is useful in finding the **complement of Boolean function**. It states that the complement of logical OR of at least two Boolean variables is equal to the logical AND of each complemented variable.

DeMorgan's theorem with 2 Boolean variables x and y can be represented as

$$(x + y)' = x'.y'$$

The dual of the above Boolean function is

$$(x.y)' = x' + y'$$

Therefore, the complement of logical AND of two Boolean variables is equal to the logical OR of each complemented variable. Similarly, we can apply DeMorgan's theorem for more than 2 Boolean variables also.

### **Simplification of Boolean Functions**

Till now, we discussed the postulates, basic laws and theorems of Boolean algebra. Now, let us simplify some Boolean functions.

#### Eg

Let us **simplify** the Boolean function, f = p'qr + pq'r + pqr' + pqr

We can simplify this function in two methods.

#### Method 1

Given Boolean function, f = p'qr + pq'r + pqr' + pqr.

**Step 1** – In first and second terms r is common and in third and fourth terms pq is common. So, take the common terms by using **Distributive law**.

$$\Rightarrow$$

f = (p'q + pq')r + pq(r' + r)

**Step 2** – The terms present in first parenthesis can be simplified to Ex-OR operation. The terms present in second parenthesis can be simplified to '1' using **Boolean postulate**

$$\Rightarrow$$

f = (p  $\bigoplus$ q)r + pq(1)

Step 3 – The first term can't be simplified further. But, the second term can be simplified to pq using Boolean postulate.

$$\Rightarrow$$

f = (p  $\bigoplus$ q)r + pq

Therefore, the simplified Boolean function is  $\mathbf{f} = (\mathbf{p} \oplus \mathbf{q})\mathbf{r} + \mathbf{p}\mathbf{q}$

#### Method 2

Given Boolean function, f = p'qr + pq'r + pqr' + pqr.

**Step 1** – Use the **Boolean postulate**, x + x = x. That means, the Logical OR operation with any Boolean variable 'n' times will be equal to the same variable. So, we can write the last term pqr two more times.

$$\Rightarrow$$

f = p'qr + pq'r + pqr' + pqr + pqr + pqr

**Step 2** – Use **Distributive law** for 1<sup>st</sup> and 4<sup>th</sup> terms, 2<sup>nd</sup> and 5<sup>th</sup> terms, 3<sup>rd</sup> and 6<sup>th</sup> terms.

$$\Rightarrow f = qr(p' + p) + pr(q' + q) + pq(r' + r)$$

**Step 3** – Use **Boolean postulate**, x + x' = 1 for simplifying the terms present in each parenthesis.

$$\Rightarrow$$

f = qr(1) + pr(1) + pq(1)

**Step 4** – Use **Boolean postulate**, x.1 = x for simplifying the above three terms.

$$\Rightarrow f = qr + pr + pq$$

$\Rightarrow$  f = pq + qr + pr

Therefore, the simplified Boolean function is  $\mathbf{f} = \mathbf{pq} + \mathbf{qr} + \mathbf{pr}$ .

So, we got two different Boolean functions after simplifying the given Boolean function in each method. Functionally, those two Boolean functions are same. So, based on the requirement, we can choose one of those two Boolean functions.

#### $\mathbf{E}\mathbf{g}$

Let us find the **complement** of the Boolean function, f = p'q + pq'.

The complement of Boolean function is f' = (p'q + pq')'.

Step 1 – Use DeMorgan's theorem, (x + y)' = x'.y'.

$$\Rightarrow$$

f' = (p'q)'.(pq')'

**Step 2** – Use DeMorgan's theorem, (x.y)' = x' + y'

$$\Rightarrow$$

f' = {(p')' + q'}.{p' + (q')'}

**Step3** – Use the Boolean postulate, (x')'=x.

$$\Rightarrow$$

f' = {p + q'}.{p' + q}

$$\Rightarrow$$

f' = pp' + pq + p'q' + qq'

**Step 4** – Use the Boolean postulate, xx'=0.

$$\Rightarrow f = 0 + pq + p'q' + 0$$

$$\Rightarrow f = pq + p'q'$$

Therefore, the **complement** of Boolean function, p'q + pq' is pq + p'q'.

## **Sum of product Method(SOP)**

A canonical sum of products is a boolean expression that entirely consists of minterms. The Boolean function F is defined on two variables X and Y. The X and Y are the inputs of the boolean function F whose output is true when any one of the inputs is set to true. The truth table for Boolean expression F is as follows:

| Inputs |   | Output |

|--------|---|--------|

| X      | Y | F      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 1      |

we can form the minterm from the variable's value. Now, a column will be added for the minterm in the above table. The complement of the variables is taken whose value is 0, and the variables whose value is 1 will remain the same.

| Inputs |   | Output | Minterm |

|--------|---|--------|---------|

| X      | Y | F      | M       |

| 0      | 0 | 0      | X'Y'    |

| 0      | 1 | 1      | X'Y     |

| 1      | 0 | 1      | XY'     |

| 1      | 1 | 1      | XY      |

Now, we will add all the minterms for which the output is true to find the desired canonical SOP(Sum of Product) expression.

## **Converting Sum of Products (SOP) to shorthand notation**

The process of converting SOP form to shorthand notation is the same as the process of finding shorthand notation for minterms. There are the following steps to find the shorthand notation of the given SOP expression.

- o Write the given SOP expression.

- o Find the shorthand notation of all the minterms.

- o Replace the minterms with their shorthand notations in the given expression.

## Example: F = X'Y + XY' + XY

1. Firstly, we write the SOP expression:

$$F = X'Y + XY' + XY$$

2. Now, we find the shorthand notations of the minterms X'Y, XY', and XY.

$$X'Y = (01)_2 = m_1$$

$$XY' = (10)_2 = m_2$$

$$XY = (11)_2 = m_3$$

3. In the end, we replace all the minterms with their shorthand notations:

F=m1+m2+m3

# **Converting shorthand notation to SOP expression**

The process of converting shorthand notation to SOP is the reverse process of converting SOP expression to shorthand notation. Let's see an example to understand this conversion.

# **Example:**

Let us assume that we have a boolean function F, which defined on two variables X and Y. The minterms for the function F are expressed as shorthand notation is as follows:

$$F = \sum (1,2,3)$$

Now, from this expression, we will find the SOP expression. The Boolean function F has two input variables X and y and the output of F=1 for m1, m2, and m3, i.e., 1<sup>st</sup>, 2<sup>nd</sup>, and 3<sup>rd</sup> combinations. So,

$$F=\sum(1,2,3)$$

$F= m1 + m2 + m3$

$F= 01 + 10 + 11$

Now, we replace zeros with either X' or Y' and ones with either X or Y. Simply, the complement variable is used when the variable value is 1 otherwise the non-complement variable is used.

$$F = \sum (1,2,3)$$

$$F=01+10+11$$

$$F= A'B + AB' + AB$$

# Karnaugh Map(K-Map) method

**Karnaugh** introduced a method for simplification of Boolean functions in an easy way. This method is known as Karnaugh map method or K-map method. It is a graphical method, which consists of 2<sup>n</sup> cells for 'n' variables. The adjacent cells are differed only in single bit position.

## K-Maps for 2 to 5 Variables

K-Map method is most suitable for minimizing Boolean functions of 2 variables to 5 variables. Now, let us discuss about the K-Maps for 2 to 5 variables one by one.

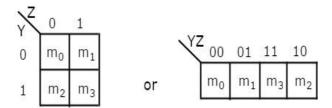

## 2 Variable K-Map

The number of cells in 2 variable K-map is four, since the number of variables is two. The following figure shows **2 variable K-Map**.

- There is only one possibility of grouping 4 adjacent min terms.

- The possible combinations of grouping 2 adjacent min terms are  $\{(m_0, m_1), (m_2, m_3), (m_0, m_2) \text{ and } (m_1, m_3)\}$ .

## 3 Variable K-Map

The number of cells in 3 variable K-map is eight, since the number of variables is three. The following figure shows **3 variable K-Map**.

| XX | 00             | 01             | 11             | 10             |

|----|----------------|----------------|----------------|----------------|

| 0  | m <sub>0</sub> | $m_1$          | m <sub>3</sub> | m <sub>2</sub> |

| 1  | m <sub>4</sub> | m <sub>5</sub> | m <sub>7</sub> | m <sub>6</sub> |

- There is only one possibility of grouping 8 adjacent min terms.

- The possible combinations of grouping 4 adjacent min terms are {(m<sub>0</sub>, m<sub>1</sub>, m<sub>3</sub>, m<sub>2</sub>), (m<sub>4</sub>, m<sub>5</sub>, m<sub>7</sub>, m<sub>6</sub>), (m<sub>0</sub>, m<sub>1</sub>, m<sub>4</sub>, m<sub>5</sub>), (m<sub>1</sub>, m<sub>3</sub>, m<sub>5</sub>, m<sub>7</sub>), (m<sub>3</sub>, m<sub>2</sub>, m<sub>7</sub>, m<sub>6</sub>) and (m<sub>2</sub>, m<sub>0</sub>, m<sub>6</sub>, m<sub>4</sub>)}.

- The possible combinations of grouping 2 adjacent min terms are {(m<sub>0</sub>, m<sub>1</sub>), (m<sub>1</sub>, m<sub>3</sub>), (m<sub>3</sub>, m<sub>2</sub>), (m<sub>2</sub>, m<sub>0</sub>), (m<sub>4</sub>, m<sub>5</sub>), (m<sub>5</sub>, m<sub>7</sub>), (m<sub>7</sub>, m<sub>6</sub>), (m<sub>6</sub>, m<sub>4</sub>), (m<sub>0</sub>, m<sub>4</sub>), (m<sub>1</sub>, m<sub>5</sub>), (m<sub>3</sub>, m<sub>7</sub>) and (m<sub>2</sub>, m<sub>6</sub>)}.

- If x=0, then 3 variable K-map becomes 2 variable K-map.

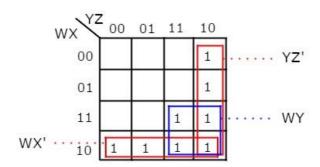

#### 4 Variable K-Map

The number of cells in 4 variable K-map is sixteen, since the number of variables is four. The following figure shows **4 variable K-Map**.

| wx YZ | 00              | 01              | 11              | 10              |

|-------|-----------------|-----------------|-----------------|-----------------|

| 00    | m <sub>0</sub>  | m <sub>1</sub>  | m <sub>3</sub>  | m <sub>2</sub>  |

| 01    | m <sub>4</sub>  | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| 10    | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> |

- There is only one possibility of grouping 16 adjacent min terms.

- Let R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and R<sub>4</sub> represents the min terms of first row, second row, third row and fourth row respectively. Similarly, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub> represents the min terms of first column, second column, third column and fourth column respectively. The possible combinations of grouping 8 adjacent min terms are {(R<sub>1</sub>, R<sub>2</sub>), (R<sub>2</sub>, R<sub>3</sub>), (R<sub>3</sub>, R<sub>4</sub>), (R<sub>4</sub>, R<sub>1</sub>), (C<sub>1</sub>, C<sub>2</sub>), (C<sub>2</sub>, C<sub>3</sub>), (C<sub>3</sub>, C<sub>4</sub>), (C<sub>4</sub>, C<sub>1</sub>)}.

- If w=0, then 4 variable K-map becomes 3 variable K-map.

### 5 Variable K-Map

The number of cells in 5 variable K-map is thirty-two, since the number of variables is 5. The following figure shows **5 variable K-Map**.

| V=0   |                 |                 |                 |                 | V= | =1              |                 |                 |                 |

|-------|-----------------|-----------------|-----------------|-----------------|----|-----------------|-----------------|-----------------|-----------------|

| WX YZ | 00              | 01              | 11              | 10              | WX | 00              | 01              | 11              | 10              |

| 00    | m <sub>0</sub>  | m <sub>1</sub>  | m <sub>3</sub>  | m <sub>2</sub>  | 00 | m <sub>16</sub> | m <sub>17</sub> | m <sub>19</sub> | m <sub>18</sub> |

| 01    | m <sub>4</sub>  | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  | 01 | m <sub>20</sub> | m <sub>21</sub> | m <sub>23</sub> | m <sub>22</sub> |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> | 11 | m <sub>28</sub> | m <sub>29</sub> | m <sub>31</sub> | m <sub>30</sub> |

| 10    | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> | 10 | m <sub>24</sub> | m <sub>25</sub> | m <sub>27</sub> | m <sub>26</sub> |

- There is only one possibility of grouping 32 adjacent min terms.

- There are two possibilities of grouping 16 adjacent min terms. i.e., grouping of min terms from m<sub>0</sub> to m<sub>15</sub> and m<sub>16</sub> to m<sub>31</sub>.

- If v=0, then 5 variable K-map becomes 4 variable K-map.

In the above all K-maps, we used exclusively the min terms notation. Similarly, you can use exclusively the Max terms notation.

## Minimization of Boolean Functions using K-Maps

If we consider the combination of inputs for which the Boolean function is '1', then we will get the Boolean function, which is in **standard sum of products** form after simplifying the K-map.

Similarly, if we consider the combination of inputs for which the Boolean function is '0', then we will get the Boolean function, which is in **standard product of sums** form after simplifying the K-map.

Follow these rules for simplifying K-maps in order to get standard sum of products form.

- Select the respective K-map based on the number of variables present in the Boolean function.

- If the Boolean function is given as sum of min terms form, then place the ones at respective min term cells in the K-map. If the Boolean function is given as sum of products form, then place the ones in all possible cells of K-map for which the given product terms are valid.

- Check for the possibilities of grouping maximum number of adjacent ones. It should be powers of two. Start from highest power of two and upto least power of two. Highest power is equal to the number of variables considered in K-map and least power is zero.

- Each grouping will give either a literal or one product term. It is known as **prime implicant**. The prime implicant is said to be **essential prime implicant**, if atleast single '1' is not covered with any other groupings but only that grouping covers.

- Note down all the prime implicants and essential prime implicants. The simplified Boolean function contains all essential prime implicants and only the required prime implicants.

Note 1 – If outputs are not defined for some combination of inputs, then those output values will be represented with **don't care symbol 'x'**. That means, we can consider them as either '0' or '1'.

**Note 2** – If don't care terms also present, then place don't cares 'x' in the respective cells of K-map. Consider only the don't cares 'x' that are helpful for grouping maximum number of adjacent ones. In those cases, treat the don't care value as '1'.

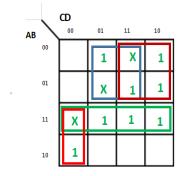

#### Eg

Let us **simplify** the following Boolean function, f(W, X, Y, Z) = WX'Y' + WY + W'YZ' using K-map.

The given Boolean function is in sum of products form. It is having 4 variables W, X, Y & Z. So, we require **4 variable K-map**. The **4 variable K-map** with ones corresponding to the given product terms is shown in the following figure.

| WX YZ | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    |    |    |    | 1  |

| 01    |    |    |    | 1  |

| 11    |    |    | 1  | 1  |

| 10    | 1  | 1  | 1  | 1  |

Here, 1s are placed in the following cells of K-map.

- The cells, which are common to the intersection of Row 4 and columns 1 & 2 are corresponding to the product term, WX'Y'.

- The cells, which are common to the intersection of Rows 3 & 4 and columns 3 & 4 are corresponding to the product term, **WY**.

- The cells, which are common to the intersection of Rows 1 & 2 and column 4 are corresponding to the product term, W'YZ'.

There are no possibilities of grouping either 16 adjacent ones or 8 adjacent ones. There are three possibilities of grouping 4 adjacent ones. After these three groupings, there is no single one left as ungrouped. So, we no need to check for grouping of 2 adjacent ones. The 4 variable K-map with these three groupings is shown in the following figure.

Here, we got three prime implicants WX', WY & YZ'. All these prime implicants are **essential** because of following reasons.

- Two ones (ms & m9) of fourth row grouping are not covered by any other groupings. Only fourth row grouping covers those two ones.

- Single one (**m**<sub>15</sub>) of square shape grouping is not covered by any other groupings. Only the square shape grouping covers that one.

- Two ones  $(m_2 \& m_6)$  of fourth column grouping are not covered by any other groupings. Only fourth column grouping covers those two ones.

Therefore, the simplified Boolean function is

$$f = WX' + WY + YZ'$$

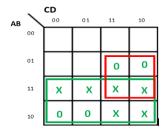

Follow these rules for simplifying K-maps in order to get standard product of sums form.

- Select the respective K-map based on the number of variables present in the Boolean function.

- If the Boolean function is given as product of Max terms form, then place the zeroes at respective Max term cells in the K-map. If the Boolean function is given as product of sums form, then place the zeroes in all possible cells of K-map for which the given sum terms are valid.

- Check for the possibilities of grouping maximum number of adjacent zeroes. It should be powers of two. Start from highest power of two and upto least power of two. Highest power is equal to the number of variables considered in K-map and least power is zero.

- Each grouping will give either a literal or one sum term. It is known as **prime implicant**. The prime implicant is said to be **essential prime implicant**, if atleast single '0' is not covered with any other groupings but only that grouping covers.

- Note down all the prime implicants and essential prime implicants. The simplified Boolean function contains all essential prime implicants and only the required prime implicants.

**Note** – If don't care terms also present, then place don't cares 'x' in the respective cells of K-map. Consider only the don't cares 'x' that are helpful for grouping maximum number of adjacent zeroes. In those cases, treat the don't care value as '0'.

## Pair, Quad and Octet

<u>Pair Reduction Rule</u>: Remove the variable which changes its state from complemented to uncomplemented or vice versa. Pair removes one variable only.

| X  | yz | y'z'<br>00 | y'z<br>01 | yz<br>11 | yz'<br>10 |

|----|----|------------|-----------|----------|-----------|

| x' | 0  | 0          | 0         | 1        | 1         |

| Х  | 1  | 1          | 1         | 0        | 0         |

<u>Quad Reduction Rule</u>: Remove the two variables which change their states. A quad removes two variables.

| ab      | c'd'<br>00 | c'd<br>01 | cd<br>11 | cd'<br>10 |

|---------|------------|-----------|----------|-----------|

| a'b' 00 | 1          | 1         | 0        | 1         |

| a'b 01  | 1          | 1         | 0        | 0         |

| ab 11   | 0          | 0         | 1        | 0         |

| ab' 10  | 0          | 1         | 0        | 0         |

<u>Octet Reduction Rule</u>: Remove the three variables which changes their state. Octet removes three variables.

| ab      | c'd'<br>00 |   |   | cd'<br>10 |

|---------|------------|---|---|-----------|

| a'b' 00 | 0          | 1 | 1 | 1         |

| a'b 01  | 0          | 1 | 1 | 0         |

| ab 11   | 0          | 1 | 1 | 0         |

| ab' 10  | 0          | 1 | 1 | 0         |

<u>Map Rolling</u>: Map rolling means roll the map considering the map as if its left edges are touching the right edges and top edges are touching bottom edges. While marking the pairs quads and octet, map must be rolled.

| x yz | y'z'<br>00 | y'z<br>01 | yz<br>11 | yz'<br>10 | x yz | y'z'<br>00 | y'z<br>01 | yz<br>11 | yz'<br>10 |

|------|------------|-----------|----------|-----------|------|------------|-----------|----------|-----------|

| x' 0 | 0          | 1         | 1        | 0         | x' 0 | 1          | 0         | 0        | 1         |

| x 1  | 1          | 0         | 0        | 1         | x 1  | 1          | 0         | 0        | 1         |

<u>Overlapping Groups</u>: Overlapping means same 1 can be encircled more than once. Overlapping always leads to simpler expressions.

| X  | yz y'z'<br>00 |   | y'z<br>01 | yz<br>11 | yz'<br>10 |

|----|---------------|---|-----------|----------|-----------|

| x' | 0             | 1 | 1         | 0        | 0         |

| х  | 1             | 0 | 1         | 0        | 0         |

**<u>Redundant Group</u>**: It is a group whose all 1's are overlapped by other groups. Redundant groups must be removed. Removal of redundant group leads to much simpler expression.

| X  | yz | y'z'<br>00 | y'z<br>01 | yz<br>11 | yz'<br>10 |

|----|----|------------|-----------|----------|-----------|

| χ' | 0  | 1          | 1         | 0        | 0         |

| х  | 1  | 0          | 1         | 1        | 0         |

**Eg**: Represent the following boolean expression in a K-map and simplify.

$$F = x'yz + x'yz' + xy'z' + xy'z$$

## **Solution**:

The K-map is as follows:

| X  | yz | y'z'<br>00 | y'z<br>01 | yz<br>11 | yz'<br>10 |

|----|----|------------|-----------|----------|-----------|

| χ′ | 0  | 0          | 0         | 1        | 1         |

| Х  | 1  | 1          | 1         | 0        | 0         |

Hence the simplified expression is

$$F = x'y + xy'$$

**Ex. 2**: Simplify the following boolean expression using K-map.

$$F = a'bc + ab'c' + abc + abc'$$

#### **Solution:**

The K-map is as follows:

| a  | bc | b'c'<br>00 | b'c<br>01 | bc<br>11 | bc'<br>10 |

|----|----|------------|-----------|----------|-----------|

| a' | 0  | 0          | 0         | 1        | 0         |

| а  | 1  | 1          | 0         | 1        | 1         |

Hence the simplified expression is

$$F = bc + ac'$$

### **Don't Care Condition**

The "Don't Care" conditions allow us to replace the empty cell of a K-Map to form a grouping of the variables. While forming groups of cells, we can consider a "Don't Care" cell as either 1 or 0 or we can simply ignore that cell. Therefore, "Don't Care" condition can help us to form a larger group of cells.

A Don't Care cell can be represented by a cross(X) in K-Maps representing a invalid combination. For example, in Excess-3 code system, the states 0000, 0001, 0010, 1101, 1110 and 1111 are invalid or unspecified. These are called don't cares. Also, in design of 4-bit BCD-to-XS-3 code converter, the input combinations 1010, 1011, 1100, 1101, 1110, and 1111 are don't cares.

A standard SOP function having don't cares can be converted into a POS expression by keeping don't cares as they are, and writing the missing minterms of the SOP form as the maxterm of POS form. Similarly, a POS function having don't cares can be converted to SOP form keeping the don't cares as they are and write the missing maxterms of the POS expression as the minterms of SOP expression.

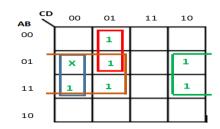

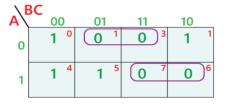

Eg

Minimise the following function in SOP minimal form using K-Maps:

$$f = m(1, 5, 6, 12, 13, 14) + d(4)$$

## **Explanation**

The SOP K-map for the given expression is:

Therefore, SOP minimal is,

$$f = BC' + BD' + A'C'D$$

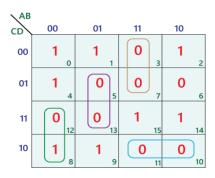

### $\mathbf{E}\mathbf{g}$

Minimise the following function in SOP minimal form using K-Maps:

$$F(A, B, C, D) = m(0, 1, 2, 3, 4, 5) + d(10, 11, 12, 13, 14, 15)$$

## **Explanation:**

Writing the given expression in POS form:

$$F(A, B, C, D) = M(6, 7, 8, 9) + d(10, 11, 12, 13, 14, 15)$$

The POS K-map for the given expression is:

Therefore, POS minimal is,

$$F = A'(B' + C')$$

# $\mathbf{E}\mathbf{g}$

Minimise the following function in SOP minimal form using K-Maps: F(A, B, C, D) = m(1, 2, 6, 7, 8, 13, 14, 15) + d(3, 5, 12)

## **Explanation:**

The SOP K-map for the given expression is:

$$f = AC'D' + A'D + A'C + AB$$

# **Product of Sum Method(POS)**

A canonical product of sum is a boolean expression that entirely consists of maxterms. The Boolean function F is defined on two variables X and Y. The X and Y are the inputs of the boolean function F whose output is true when only one of the inputs is set to true. The truth table for Boolean expression F is as follows:

| Inputs |   | Output |  |  |

|--------|---|--------|--|--|

| X      | Y | F      |  |  |

| 0      | 0 | 0      |  |  |

| 0      | 1 | 1      |  |  |

| 1      | 0 | 1      |  |  |

| 1      | 1 | 0      |  |  |

In our minterm and maxterm section, we learned about how we can form the maxterm from the variable's value. A column will be added for the maxterm in the above table. The complement of the variables is taken whose value is 0, and the variables whose value is 1 will remain the same.

| Inputs |   | Output | Minterm |

|--------|---|--------|---------|

| X      | Y | F      | M       |

| 0      | 0 | 0      | X'+Y'   |

| 0      | 1 | 1      | X'+Y    |

| 1      | 0 | 1      | X+Y'    |

| 1      | 1 | 1      | X+Y     |

Now, we will multiply all the minterms for which the output is false to find the desired canonical POS(Product of sum) expression.

$$F=(X'+Y').(X+Y)$$

### **Converting Product of Sum (POS) to shorthand notation**

The process of converting POS form to shorthand notation is the same as the process of finding shorthand notation for maxterms. There are the following steps used to find the shorthand notation of the given POS expression.

- o Write the given POS expression.

- o Find the shorthand notation of all the maxterms.

- o Replace the minterms with their shorthand notations in the given expression.

### **Eg**

$$\mathbf{F} = (\mathbf{X'+Y'}).(\mathbf{X+Y})$$

1. Firstly, we will write the POS expression:

$$F = (X'+Y').(X+Y)$$

2. Now, we will find the shorthand notations of the maxterms X'+Y' and X+Y.

$$X'+Y'=(00)_2=M_0$$

$$X+Y = (11)_2 = M_3$$

3. In the end, we will replace all the minterms with their shorthand notations:

$F=M_0.M_3$

## **Converting shorthand notation to POS expression**

The process of converting shorthand notation to POS is the reverse process of converting POS expression to shorthand notation. Let's see an example to understand this conversion.

#### Eg

Let us assume that we have a boolean function F, defined on two variables X and Y. The maxterms for the function F are expressed as shorthand notation is as follows:

$$F = \prod (1,2,3)$$

Now, from this expression, we find the POS expression. The Boolean function F has two input variables X and Y and the output of F=0 for M1, M2, and M3, i.e., 1<sup>st</sup>, 2<sup>nd</sup>, and 3<sup>rd</sup> combinations. So,

$$F=\prod(1,2,3)$$

$F=M1.M2.M3$

$F=01.10.11$

Next, we replace zeros with either X or Y and ones with either X' or Y'. Simply, if the value of the variable is 1, then we take the complement of that variable, and if the value of the variable is 0, then we take the variable "as is".

$$F = \sum (1,2,3)$$

$$F=01.10.11$$

$$F=(A+B').(A'+B).(A'+B')$$

## **Product of Sum Simplification**

To find the simplified maxterm solution using K-map is the same as to find for the minterm solution. There are some minor changes in the maxterm solution, which are as follows:

- 1. We will populate the K-map by entering the value of 0 to each sum-term into the K-map cell and fill the remaining cells with one's.

- 2. We will make the groups of 'zeros' not for 'ones'.

- 3. Now, we will define the boolean expressions for each group as sum-terms.

- 4. At last, to find the simplified boolean expression in the POS form, we will combine the sum-terms of all individual groups.

Let's take some example of 2-variable, 3-variable, 4-variable and 5-variable K-map examples

## Eg

$$Y=(A'+B')+(A'+B)+(A+B)$$

Simplified expression: A'B

## Eg

$$Y=(A + B + C') + (A + B' + C') + (A' + B' + C) + (A' + B' + C')$$

Simplified expression:  $Y=(A + C') \cdot (A' + B')$

## <u>Eg</u>

## $F(A,B,C,D)=\pi(3,5,7,8,10,11,12,13)$

Simplified expression:  $Y=(A + C') \cdot (A' + B')$

## **Data Processing Circuit**

## **Multiplexer**

**Multiplexer** is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines.

Since there are 'n' selection lines, there will be  $2^n$  possible combinations of zeros and ones. So, each combination will select only one data input. Multiplexer is also called as  $\mathbf{Mux}$ .

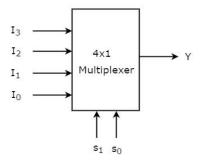

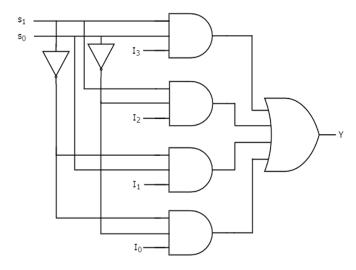

## **4x1 Multiplexer**

4x1 Multiplexer has four data inputs  $I_3$ ,  $I_2$ ,  $I_1$  &  $I_0$ , two selection lines  $s_1$  &  $s_0$  and one output Y. The **block diagram** of 4x1 Multiplexer is shown in the following figure.

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines. **Truth table** of 4x1 Multiplexer is shown below.

| Selection | Output |       |

|-----------|--------|-------|

| $S_1$     | $S_0$  | Y     |

| 0         | 0      | $I_0$ |

| 0         | 1      | $I_1$ |

| 1 | 0 | $I_2$ |

|---|---|-------|

| 1 | 1 | $I_3$ |

From Truth table, we can directly write the **Boolean function** for output, Y as

$$Y = \{S\{1\}\} | \{S\{0\}\} | \{0\} + \{S\{1\}\} | \{S\{0\}\} | \{S\{0\}\} | \{2\} + \{S\{1\}\} | \{S\{0\}\} | \{S\{$$

We can implement this Boolean function using Inverters, AND gates & OR gate. The **circuit diagram** of 4x1 multiplexer is shown in the following figure.

We can easily understand the operation of the above circuit. Similarly, you can implement 8x1 Multiplexer and 16x1 multiplexer by following the same procedure.

## Implementation of Higher-order Multiplexers.

Now, let us implement the following two higher-order Multiplexers using lower-order Multiplexers.

- 8x1 Multiplexer

- 16x1 Multiplexer

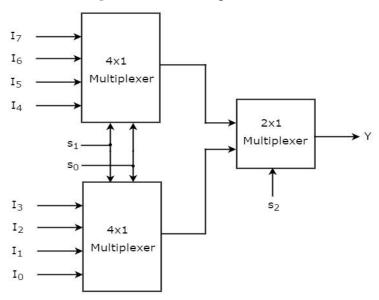

## **8x1 Multiplexer**

In this section, let us implement 8x1 Multiplexer using 4x1 Multiplexers and 2x1 Multiplexer. We know that 4x1 Multiplexer has 4 data inputs, 2 selection lines and one output. Whereas, 8x1 Multiplexer has 8 data inputs, 3 selection lines and one output.

So, we require two **4x1 Multiplexers** in first stage in order to get the 8 data inputs. Since, each 4x1 Multiplexer produces one output, we require a **2x1 Multiplexer** in second stage by considering the outputs of first stage as inputs and to produce the final output.

Let the 8x1 Multiplexer has eight data inputs  $I_7$  to  $I_0$ , three selection lines  $s_2$ ,  $s_1$  & s0 and one output Y. The **Truth table** of 8x1 Multiplexer is shown below.

| Se    | Output |       |   |

|-------|--------|-------|---|

| $S_2$ | $S_1$  | $S_0$ | Y |

| 0 | 0 | 0 | $I_0$          |

|---|---|---|----------------|

| 0 | 0 | 1 | $\mathbf{I}_1$ |

| 0 | 1 | 0 | $I_2$          |

| 0 | 1 | 1 | $I_3$          |

| 1 | 0 | 0 | $I_4$          |

| 1 | 0 | 1 | $I_5$          |

| 1 | 1 | 0 | $I_6$          |

| 1 | 1 | 1 | $I_7$          |

We can implement 8x1 Multiplexer using lower order Multiplexers easily by considering the above Truth table. The **block diagram** of 8x1 Multiplexer is shown in the following figure.

The same **selection lines, s**<sub>1</sub> & **s**<sub>0</sub> are applied to both 4x1 Multiplexers. The data inputs of upper 4x1 Multiplexer are  $I_7$  to  $I_4$  and the data inputs of lower 4x1 Multiplexer are  $I_3$  to  $I_0$ . Therefore, each 4x1 Multiplexer produces an output based on the values of selection lines,  $s_1$  &  $s_0$ .

The outputs of first stage 4x1 Multiplexers are applied as inputs of 2x1 Multiplexer that is present in second stage. The other **selection line**, **s**<sub>2</sub> is applied to 2x1 Multiplexer.

- If  $s_2$  is zero, then the output of 2x1 Multiplexer will be one of the 4 inputs  $I_3$  to  $I_0$  based on the values of selection lines  $s_1 & s_0$ .

- If  $s_2$  is one, then the output of 2x1 Multiplexer will be one of the 4 inputs  $I_7$  to  $I_4$  based on the values of selection lines  $s_1 & s_0$ .

Therefore, the overall combination of two 4x1 Multiplexers and one 2x1 Multiplexer performs as one 8x1 Multiplexer.

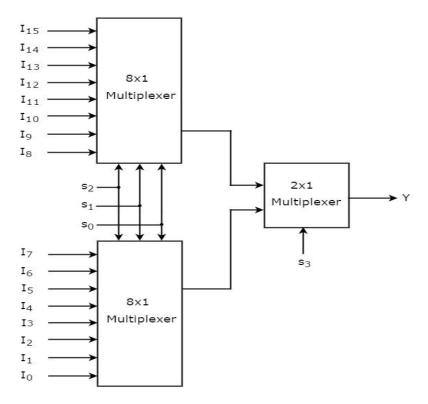

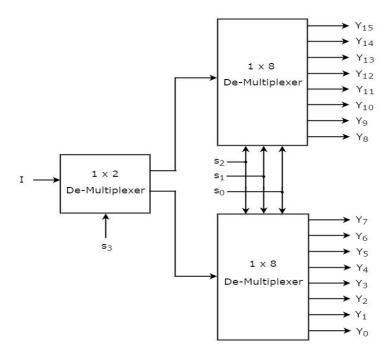

## **16x1 Multiplexer**

In this section, let us implement 16x1 Multiplexer using 8x1 Multiplexers and 2x1 Multiplexer. We know that 8x1 Multiplexer has 8 data inputs, 3 selection lines and one output. Whereas, 16x1 Multiplexer has 16 data inputs, 4 selection lines and one output.

So, we require two **8x1 Multiplexers** in first stage in order to get the 16 data inputs. Since, each 8x1 Multiplexer produces one output, we require a 2x1 Multiplexer in second stage by considering the outputs of first stage as inputs and to produce the final output.

Let the 16x1 Multiplexer has sixteen data inputs  $I_{15}$  to  $I_0$ , four selection lines  $s_3$  to  $s_0$  and one output Y. The **Truth table** of 16x1 Multiplexer is shown below.

|                | Selection      | Output         |    |                 |

|----------------|----------------|----------------|----|-----------------|

| S <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | So | Y               |

| 0              | 0              | 0              | 0  | $I_0$           |

| 0              | 0              | 0              | 1  | $\mathbf{I}_1$  |

| 0              | 0              | 1              | 0  | $I_2$           |

| 0              | 0              | 1              | 1  | $I_3$           |

| 0              | 1              | 0              | 0  | $I_4$           |

| 0              | 1              | 0              | 1  | I <sub>5</sub>  |

| 0              | 1              | 1              | 0  | $I_6$           |

| 0              | 1              | 1              | 1  | $I_7$           |

| 1              | 0              | 0              | 0  | $I_8$           |

| 1              | 0              | 0              | 1  | <b>I</b> 9      |

| 1              | 0              | 1              | 0  | $I_{10}$        |

| 1              | 0              | 1              | 1  | $I_{11}$        |

| 1              | 1              | 0              | 0  | $I_{12}$        |

| 1              | 1              | 0              | 1  | I <sub>13</sub> |

| 1              | 1              | 1              | 0  | I <sub>14</sub> |

| 1              | 1              | 1              | 1  | I <sub>15</sub> |

We can implement 16x1 Multiplexer using lower order Multiplexers easily by considering the above Truth table. The **block diagram** of 16x1 Multiplexer is shown in the following figure.

The same selection lines,  $s_2$ ,  $s_1$  &  $s_0$  are applied to both 8x1 Multiplexers. The data inputs of upper 8x1 Multiplexer are  $I_{15}$  to  $I_8$  and the data inputs of lower 8x1 Multiplexer are  $I_7$  to  $I_9$ . Therefore, each 8x1 Multiplexer produces an output based on the values of selection lines,  $s_2$ ,  $s_1$  &  $s_9$ .

The outputs of first stage 8x1 Multiplexers are applied as inputs of 2x1 Multiplexer that is present in second stage. The other **selection line**, **s**<sub>3</sub> is applied to 2x1 Multiplexer.

- If  $s_3$  is zero, then the output of 2x1 Multiplexer will be one of the 8 inputs  $Is_7$  to  $I_0$  based on the values of selection lines  $s_2$ ,  $s_1$  &  $s_0$ .

- If  $s_3$  is one, then the output of 2x1 Multiplexer will be one of the 8 inputs  $I_{15}$  to  $I_8$  based on the values of selection lines  $s_2$ ,  $s_1$  &  $s_0$ .

Therefore, the overall combination of two 8x1 Multiplexers and one 2x1 Multiplexer performs as one 16x1 Multiplexer.

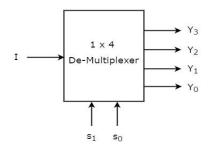

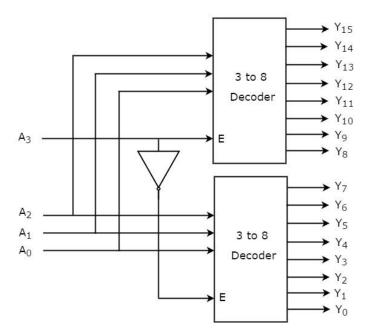

#### **De-Multiplexer**

**De-Multiplexer** is a combinational circuit that performs the reverse operation of Multiplexer. It has single input, 'n' selection lines and maximum of  $2^n$  outputs. The input will be connected to one of these outputs based on the values of selection lines.

Since there are 'n' selection lines, there will be 2<sup>n</sup> possible combinations of zeros and ones. So, each combination can select only one output. De-Multiplexer is also called as **De-Mux**.

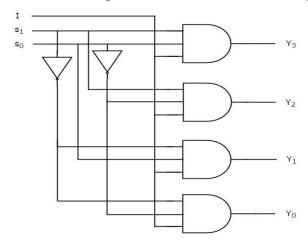

#### 1x4 De-Multiplexer

1x4 De-Multiplexer has one input I, two selection lines,  $s_1 \& s_0$  and four outputs  $Y_3$ ,  $Y_2$ ,  $Y_1 \& Y_0$ . The **block diagram** of 1x4 De-Multiplexer is shown in the following figure.

The single input 'I' will be connected to one of the four outputs,  $Y_3$  to  $Y_0$  based on the values of selection lines  $s_1$  &  $s_0$ . The **Truth table** of 1x4 De-Multiplexer is shown below.

| Selection      | Outputs          |            |            |            |    |

|----------------|------------------|------------|------------|------------|----|

| S <sub>1</sub> | $\mathbf{S}_{0}$ | <b>Y</b> 3 | <b>Y</b> 2 | <b>Y</b> 1 | Yo |

| 0              | 0                | 0          | 0          | 0          | I  |

| 0              | 1                | 0          | 0          | I          | 0  |

| 1              | 0                | 0          | I          | 0          | 0  |

| 1              | 1                | I          | 0          | 0          | 0  |

From the above Truth table, we can directly write the Boolean functions for each output as

$$Y{3}=s{1}s{0}I$$

$$Y{2}=s{1}{s{0}}'I$$

$$Y{1}={s{1}}'s{0}I$$

$$Y{0}={s1}'{s{0}}'{1}$$

We can implement these Boolean functions using Inverters & 3-input AND gates. The **circuit diagram** of 1x4 De-Multiplexer is shown in the following figure.

We can easily understand the operation of the above circuit. Similarly, you can implement 1x8 De-Multiplexer and 1x16 De-Multiplexer by following the same procedure.

## **Implementation of Higher-order De-Multiplexers**

Now, let us implement the following two higher-order De-Multiplexers using lower-order De-Multiplexers.

- 1x8 De-Multiplexer

- 1x16 De-Multiplexer

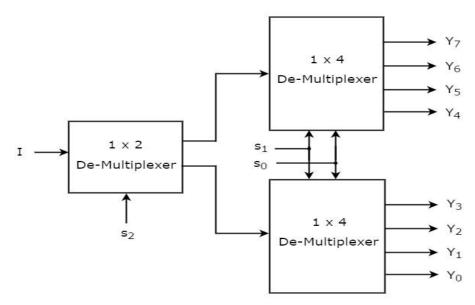

## 1x8 De-Multiplexer

In this section, let us implement 1x8 De-Multiplexer using 1x4 De-Multiplexers and 1x2 De-Multiplexer. We know that 1x4 De-Multiplexer has single input, two selection lines and four outputs. Whereas, 1x8 De-Multiplexer has single input, three selection lines and eight outputs.

So, we require two **1x4 De-Multiplexers** in second stage in order to get the final eight outputs. Since, the number of inputs in second stage is two, we require **1x2 DeMultiplexer** in first stage so that the outputs of first stage will be the inputs of second stage. Input of this 1x2 De-Multiplexer will be the overall input of 1x8 De-Multiplexer.

Let the 1x8 De-Multiplexer has one input I, three selection lines  $s_2$ ,  $s_1$  &  $s_0$  and outputs  $Y_7$  to  $Y_0$ . The **Truth table** of 1x8 De-Multiplexer is shown below.

| Sel        | ection Inp | outs |            | Outputs    |            |            |            |            |                       |    |

|------------|------------|------|------------|------------|------------|------------|------------|------------|-----------------------|----|

| <b>S</b> 2 | S1         | So   | <b>Y</b> 7 | <b>Y</b> 6 | <b>Y</b> 5 | <b>Y</b> 4 | <b>Y</b> 3 | <b>Y</b> 2 | <b>Y</b> <sub>1</sub> | Yo |

| 0          | 0          | 0    | 0          | 0          | 0          | 0          | 0          | 0          | 0                     | I  |

| 0          | 0          | 1    | 0          | 0          | 0          | 0          | 0          | 0          | I                     | 0  |

| 0          | 1          | 0    | 0          | 0          | 0          | 0          | 0          | I          | 0                     | 0  |

| 0          | 1          | 1    | 0          | 0          | 0          | 0          | I          | 0          | 0                     | 0  |

| 1          | 0          | 0    | 0          | 0          | 0          | I          | 0          | 0          | 0                     | 0  |

| 1          | 0          | 1    | 0          | 0          | I          | 0          | 0          | 0          | 0                     | 0  |

| 1          | 1          | 0    | 0          | I          | 0          | 0          | 0          | 0          | 0                     | 0  |

| 1 | 1 | 1 | I | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |   |   |

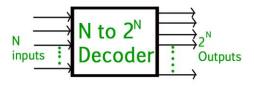

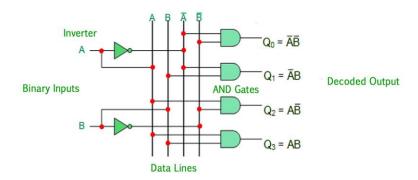

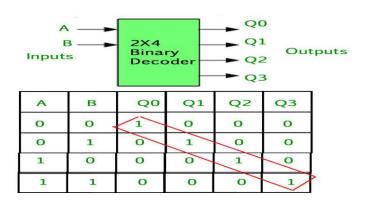

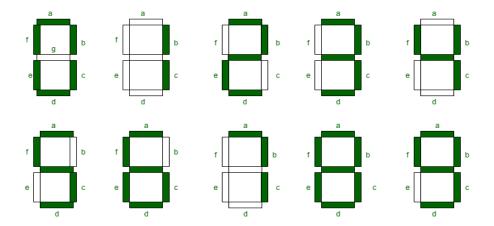

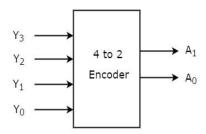

We can implement 1x8 De-Multiplexer using lower order Multiplexers easily by considering the above Truth table. The **block diagram** of 1x8 De-Multiplexer is shown in the following figure.